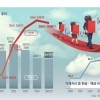

세계로 달린다 일류를 향하여/세계 반도체시장 나노전쟁

수정 2004-01-01 00:00

입력 2004-01-01 00:00

나노(㎚)는 머리카락 굵기의 8만분의 1에 해당하는 10억분의 1m를 나타내는 단위.반도체 공정에서는 칩속에 복잡하게 얽혀 있는 회로의 간격을 좁히는 게 수율 향상의 관건이다.현재 반도체 선두업체들이 나노급 공정을 활용,치열하게 회로선폭 ‘좁히기’ 경쟁을 벌이고 있다.

삼성전자가 지난해 9월말 세계 최초로 70나노 공정을 활용한 4기가 난드(NAND·데이터저장형) 플래시메모리를 개발한데 이어 인텔도 지난해말 65나노 공정을 활용한 S램 개발에 성공했다.일본의 도시바와 소니도 최근 공동으로 65나노 칩의 양산 기술을 개발한 것으로 알려졌다.

반도체 업계에서 이처럼 나노급 공정에 매달리고 있는 것은 생산성 때문이다.대부분의 업체들은 아직 미크론(㎛·1000분의 1m)급 공정에 머물러 있거나 이제 막 나노 공정 개발에 들어간 상태다.

통상 D램을 기준으로 엄지손톱만한 크기의 칩을 0.13미크론급 공정으로 생산하면용량을 최대 256메가비트까지 담을 수 있고,0.11미크론급 공정으로는 512메가비트까지 늘릴 수 있다.나노 공정을 적용하면 용량은 기하급수적으로 커진다.90나노 공정으로는 1기가,70나노 공정으로는 4기가까지 담을 수 있다.미크론급에서는 생산성이 배씩 늘지만 나노급에서는 4배씩 늘어나는 셈이다.

반도체 업계나 학계쪽에서는 실리콘 웨이퍼를 소재로 사용하는 현재의 반도체 생산체제에서는 50∼35나노가 한계라는 지적이 있다.그보다 얇게 회로선폭을 유지하려면 신소재,신개념의 반도체가 나와야 한다는 것이다.

삼성전자는 이번 전쟁에서의 승리를 확신하고 있다.집적도 면에서 D램이 S램과 도시바·소니가 만드는 시스템LSI(비메모리)에 비해 최소한 2배 이상이기 때문에 기술의 응용이 더욱 어렵다는 것이다.다시말해 인텔이나 도시바·소니가 D램에 나노 기술을 응용하는 것은 어렵지만 삼성전자는 언제든 S램이나 비메모리쪽으로 나노 기술을 응용할 수 있다는 얘기다.

박홍환기자

2004-01-01 50면

Copyright ⓒ 서울신문 All rights reserved. 무단 전재-재배포, AI 학습 및 활용 금지